開關穩壓器的效率更高,但是電源中快速開關電晶體會產生 EMI 的問題,必須在設計中權衡考慮。本文簡述了開關穩壓器在可攜式設計中的優勢,以及透過濾波電路減輕 EMI 的重要性,並以Allegro Microsystems、Analog Devices 和 Maxim Integrated 等公司的產品為例,介紹了內置 EMI 濾波器的開關穩壓器,以及應用其簡化抑制EMI設計,最佳化高效率電源設計的方法。

對於要實現電池供電或分散式電源系統的設計人員來說,使用低壓降 (LDO) 穩壓器還是開關穩壓器往往是個問題。開關穩壓器的效率相對更高,可謂是一項優勢,尤其是對於電池供電產品。然而,電源中快速開關電晶體產生的 EMI 才是關鍵權衡要素——在高度整合的緊湊型設計中,EMI 可能會衍生成更嚴重的問題。

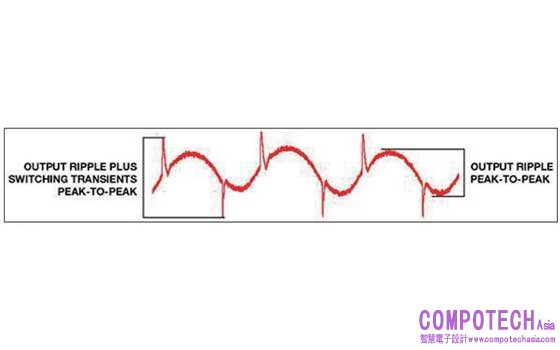

圖1:開關穩壓器的輸出電壓紋波波形圖顯示了瞬態尖峰是 EMI 的主要來源。